Home » Course Layouts » Free Course Layout Udemy

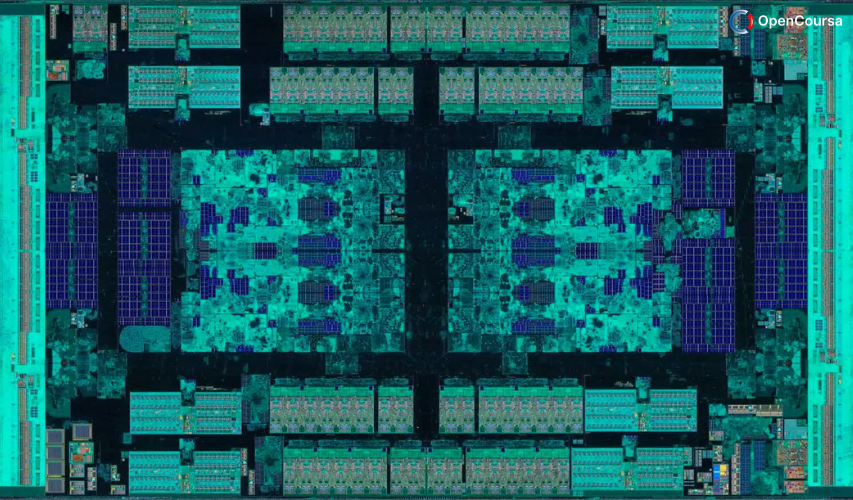

Multi-core Computer Architecture: Storage and Interconnects. Instructor: Prof. John Jose, Department of Computer Science and Engineering, IIT Guwahati.

0

1

English

English [CC]

- Learn basic syntax that can apply to any language.

- Learn what is a programming language and the basic concepts for beginners.

- Understand what is Javascript in it's truest form.

- Know the basic syntax of Javascript.

- Know some hidden quirks in Javascript.

Description

We are in the era of multi-core systems where even the simplest of handheld devices like a smartphone houses many processors in a single chip. The core counts are ever increasing from 8 to 10 in smart phones to over 100s in supercomputers. This course will introduce the students to the world of multi-core computer architectures. With the unprecedented growth of data science, on-chip storage systems and inter-core communication framework are getting equal attention as that of processors. This course will focus on delivering an in-depth exposure in memory-subsystems and interconnects of Tiled Chip Multi-Core Processors with few introductory sessions on advanced superscalar processors. The course concludes with pointers to current research standings and on-going research directions for motivating the students to explore further. (from nptel.ac.in)

Course content

-

- Lecture 01 – Introduction Unlimited

- Lecture 02 – Instruction Execution Principles Unlimited

- Lecture 03 – Introduction to Instruction Pipeline Unlimited

- Lecture 04 – Introduction to Superscalar Pipelines Unlimited

- Lecture 05 – Instruction Pipeline and Performance Unlimited

- Lecture 06 – Instruction Pipeline and Performance (cont.) Unlimited

-

- Lecture 07 – Introduction to Cache Memory Unlimited

- Lecture 08 – Block Replacement Techniques and Write Strategy Unlimited

- Lecture 09 – gem5 Simulator: An Overview Unlimited

- Lecture 10 – Cache Memory Unlimited

- Lecture 11 – Basic Cache Optimization Techniques Unlimited

- Lecture 12 – gem5 Simulator: Cache Optimization Unlimited

- Lecture 16 – Introduction to DRAM System Unlimited

- Lecture 17 – DRAM Controllers and Address Mapping Unlimited

- Lecture 18 – Address Translation Mechanisms Unlimited

- Lecture 19 – Main Memory Concepts Unlimited

- Lecture 24 – Energy Efficient Bufferless NoC Routers Unlimited

- Lecture 25 – Side-buffered Deflection Routers Unlimited

- Lecture 26 – Concepts in Network-on-Chip Unlimited

N.A

- 5 stars0

- 4 stars0

- 3 stars0

- 2 stars0

- 1 stars0

No Reviews found for this course.